HJX-AD9371-SDR

AD9371軟件無線電平台(HJX-AD9371-SDR)是我司結合 ADI 的 RadioVerseTM 技術推出的高性能(néng)SDR開(kāi)發(fā)闆。

HJX-AD9371-SDR 已入選 ADI RadioVerseTM 第三方參考設計

HJX-AD9371-SDR軟件無線電平台特點:

1. 基于合佳興成(chéng)熟的産品化設計,不僅可以測試評估AD9371芯片,更可以通過(guò)對(duì)開(kāi)發(fā)闆簡單的自定義修改,直接推出自己的産品,真正加速了設計理念到成(chéng)品的轉化過(guò)程;

2. 我們會(huì)向(xiàng)購買HJX-AD9371-SDR的用戶提供完整的能(néng)夠直接運行的FPGA源代碼、ARM源代碼、平台的原理圖以及相關的設計資料和文檔;

3. 數字、硬件和射頻的工程師人員提供技術支持。

産品詳情

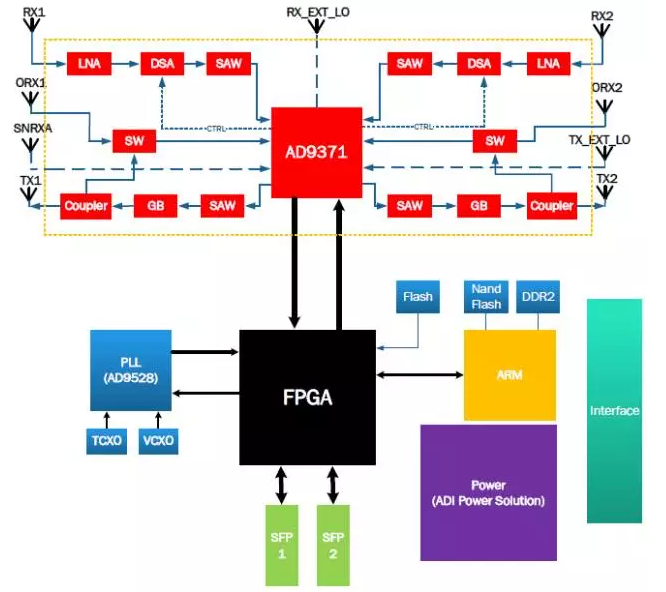

一、HJX-AD9371-SDR系統框架如下:

二、核心芯片:AD9371

1、射頻部分:采用ADI最先進(jìn)的RFTransceiverAD9371,整個RF部分具有超高的集成(chéng)度和靈活高性能(néng)的特點。該芯片支持接收100MHz、發(fā)射250MHz的帶寬以及300MHz到6GHz的RF接收發(fā)射頻率範圍。射頻鏈路上的LNA、DSA、濾波器和GAINBLOCK配合AD9371,提供了優異的系統射頻性能(néng)。同時(shí)也可通過(guò)MMCX射頻接口直接評估AD9371的射頻性能(néng)。開(kāi)發(fā)闆預留DPD反饋通道(dào)(ORX端),方便客戶自行開(kāi)發(fā)DPD算法。反饋端的射頻開(kāi)關用于啓用芯片的外部校正功能(néng),能(néng)夠獲得更好(hǎo)的本振校正性能(néng)。

四、性能(néng)測試

如下是LO及鏡像抑制指标與TDD-LTEEVM測試(更詳細的測試内容請聯系我們)

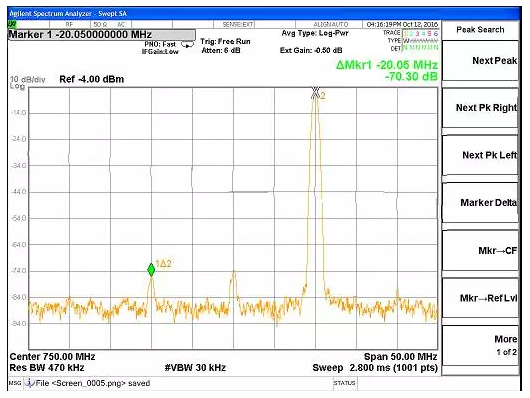

1.LO 及鏡像抑制指标

測試條件:信号源輸入單音信号功率-14dBm,經(jīng)過(guò)HJX-AD9371-SDR開(kāi)發(fā)闆後(hòu),輸出至頻譜儀的功率爲-5dBm。

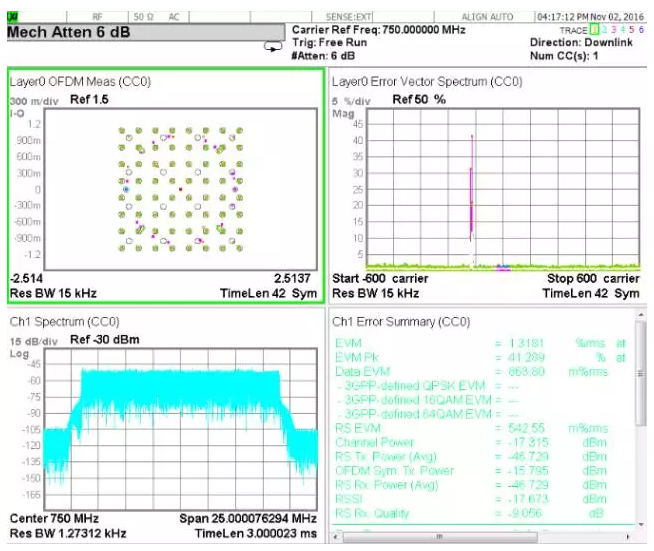

2.EVM指标

測試條件:信号源輸入20MHz TDD-LTE信号,功率爲-24dBm,經(jīng)過(guò)HJX-AD9371-SDR開(kāi)發(fā)闆後(hòu),輸出至頻譜儀的功率爲-15dBm。

- 無線直放站

- 數字光纖直放站

- 3G/4G微基站和宏基站(BTS)

- 3G/4G多載波微微蜂窩

- FDD和TDD有源天線系統

- 微波非視距(NLOS)回程系統

- 5G原型