Products

MiniTRX-Z

MiniTRX-Z

MiniTRX-Z is a low-power and small footprint board, based on ADI's RadioVerseTM technology AD9361, enables dramatic reduction in design cycles of your products.

HJX MiniTRX-Z has been added to ADI's RadioVerseTM 3rd Party Reference Designs and Hardware

Product Details

Key Features

- FPGA:Xilinx Zynq XC7Z035-2FFG676I

- DDR:512MB DDR3

- FLASH:256Mb QSPI

- SD:MicroSD

- Ethernet:10/100/1000M

- USB:USB3.0

- Communication Interface:RS232/RS422/I2C

- Sensor:Humidity Sensor with Integrated Temperature

- User Interface:GPIO

- Rx LNA range:70MHz~6GHz

- RF Digital Step Attenuator(DSA):0~31.5dB attenuation range in 0.5dB steps(1MHz to 4GHz)

- Bypass LNA and DSA to support Rx:70MHz~6.0GHz

- Size: 140mm*95mm

- Analog Devices AD9361-BBCZ Integrated RF Agile Transceiver™

RF 2 × 2 transceiver with integrated 12-bit DACs and ADCs

Band: 70 MHz to 6.0 GHz

TDD and FDD operation

Tunable channel BW:<200 kHz to 56 MHz

Supports MIMO radio: < 1 sample sync on both ADC and DAC

Miniature RF connectors – 4 TX, 4 RX, 2 TX monitor

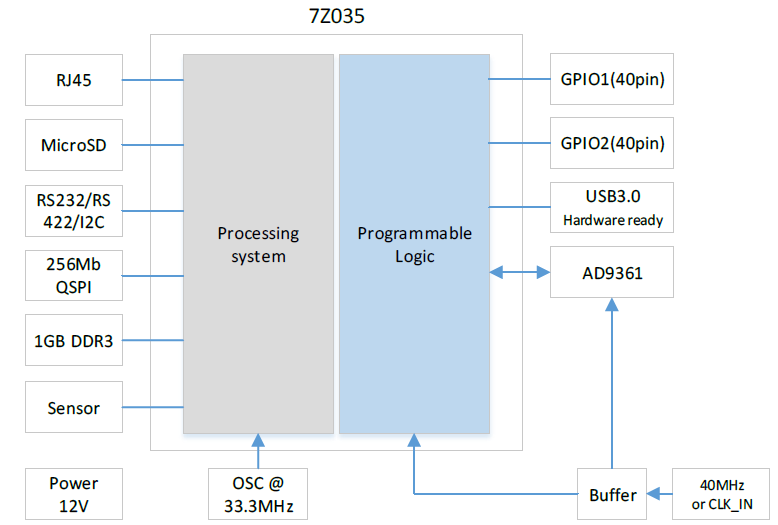

Figure2 - Simplified Block Diagram

MiniTRX-Z Getting Started Design

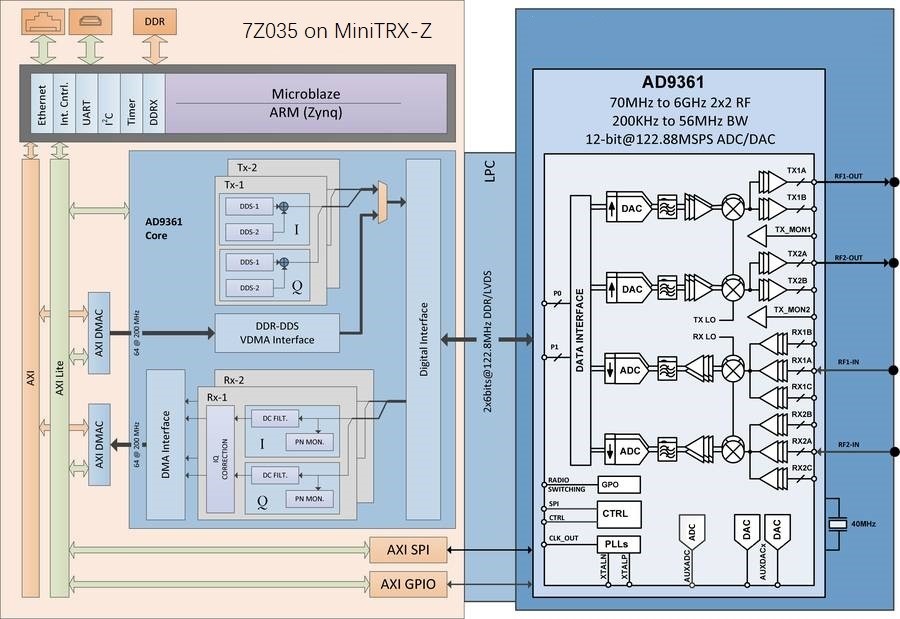

The Getting Started design implements the data interfaces to/from the AD9361 RF transceiver through which baseband signals are mixed to RF for over-the-air loopback from transmitter to receiver. Data path and control signals between the AD9361 and Zynq SoC are shown in Figure3.

- MiniTRX-Z No-OS Software: based on ADI’s AD9361 No-OS API Branch 2017_R1

Figure3 - HDL Reference Design

Figure3 - HDL Reference DesignMiniTRX-Z Interface

(1) MCX AD9361 RX1

(2) MCX AD9361 TX1

(3) MCX AD9361 TX2

(4) MCX AD9361 RX2

(5) MCX CLK_IN ( 可選外參考時(shí)鍾)

(6) JTAG

(7) Power 12V

(8) USB3.0

(9) RJ45

(10) I2C

(11) RS232

(12) RS422

(13) MicroSD

Getting Started Guide

This guide will show you how to setup MiniTRX-Z board and your computer to get started.

MiniTRX-Z Getting Started Guide v1.1.pdf

Contact Us

For more information or order products, please contact the sales office of Xiamen Hejiaxing Electronics Co.,LTD.

Mobile: +86-13600975566

WeChat:13600975566

QQ: 2355620732

Mail:zf@hjx.cn